# HALF-BRIDGE GATE DRIVER IC

#### **Features**

- Floating channel up to +600 V or +1200 V

- Soft over-current shutdown

- Synchronization signal to synchronize shutdown with the other phases

- Integrated desaturation detection circuit

- Two stage turn on output for di/dt control

- Separate pull-up/pull-down output drive pins

- · Matched delay outputs

- Undervoltage lockout with hysteresis band

- LEAD-FREE

## **Description**

The IR2114/IR2214 gate driver family is suited to drive a single half bridge in power switching applications. These drivers provide high gate driving capability (2 A source, 3 A sink) and require low quiescent current, which allows the use of bootstrap power supply techniques in medium power systems. These drivers feature full short circuit protection by means of power transistor desaturation detection and manage all half-bridge faults by smoothly turning off the desaturated transistor through the dedicated soft shutdown pin, therefore preventing over-voltages and reducing EM emissions. In multi-phase systems, the IR2114/IR2214 drivers communicate using a dedicated local network (SY\_FLT and FAULT/SD signals) to properly manage phase-to-phase short circuits. The system controller may force shutdown or read device fault state through the 3.3 V compatible CMOS I/O pin (FAULT/SD). To improve the signal immunity from DC-bus noise, the control and power ground use dedicated pins enabling low-side emitter current sensing as well. Undervoltage conditions in floating and low voltage circuits are managed independently.

## **Product Summary**

| V <sub>OFFSET</sub>                       | 600 V or<br>1200 V max. |

|-------------------------------------------|-------------------------|

| I <sub>O</sub> +/- (min)                  | 1.0 A / 1.5 A           |

| $V_{OUT}$                                 | 10.4 V – 20 V           |

| Deadtime matching (max)                   | 75 ns                   |

| Deadtime (typ)                            | 330 ns                  |

| Desat blanking time (typ)                 | 3 µs                    |

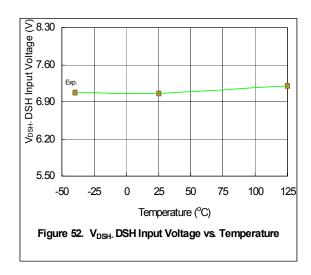

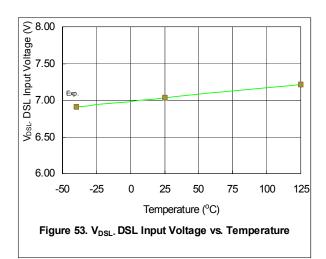

| DSH, DSL input voltage<br>threshold (typ) | 8.0 V                   |

| Soft shutdown time (typ)                  | 9.25 µs                 |

## **Package**

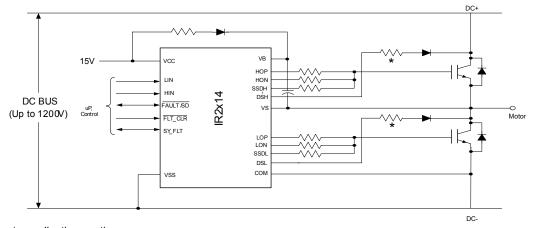

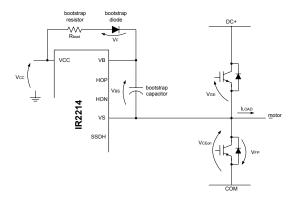

## **Typical connection**

(\*) Refer to application section

## **Absolute Maximum Ratings**

Absolute maximum ratings indicate sustained limits beyond which damage to the device may occur. All voltage parameters are absolute voltages referenced to V<sub>SS</sub>, all currents are defined positive into any lead The thermal resistance and power dissipation ratings are measured under board mounted and still air conditions.

| Symbol            | Defir                                 | Min.                  | Max.                  | Units                 |      |

|-------------------|---------------------------------------|-----------------------|-----------------------|-----------------------|------|

| Vs                | High side offset voltage              | V <sub>B</sub> - 25   | V <sub>B</sub> + 0.3  |                       |      |

| V <sub>B</sub>    | High side floating supply voltage     | IR2114                | -0.3                  | 625                   |      |

| <b>v</b> B        | Trigit side floating supply voltage   | IR2214                | -0.3                  | 1225                  |      |

| $V_{HO}$          | High side floating output voltage (H  | OP, HON and SSDH)     | V <sub>S</sub> - 0.3  | V <sub>B</sub> + 0.3  |      |

| $V_{CC}$          | Low side and logic fixed supply volt  | age                   | -0.3                  | 25                    |      |

| COM               | Power ground                          |                       | V <sub>CC</sub> - 25  | V <sub>CC</sub> + 0.3 | V    |

| $V_{LO}$          | Low side output voltage (LOP, LON     | V <sub>COM</sub> -0.3 | V <sub>CC</sub> + 0.3 |                       |      |

| $V_{\text{IN}}$   | Logic input voltage (HIN, LIN and F   | V <sub>SS</sub> -0.3  | V <sub>CC</sub> + 0.3 |                       |      |

| $V_{FLT}$         | FAULT input/output voltage (FAULT     | Г/SD and SY_FLT)      | V <sub>SS</sub> -0.3  | V <sub>CC</sub> + 0.3 |      |

| $V_{DSH}$         | High side DS input voltage            |                       | V <sub>S</sub> -3     | V <sub>B</sub> + 0.3  |      |

| $V_{DSL}$         | Low side DS input voltage             |                       | V <sub>COM</sub> -3   | V <sub>CC</sub> + 0.3 |      |

| dVs/dt            | Allowable offset voltage slew rate    |                       | _                     | 50                    | V/ns |

| $P_{D}$           | Package power dissipation @ $T_A \le$ | <u>25 °</u> C         | _                     | 1.5                   | W    |

| Rth <sub>JA</sub> | Thermal resistance, junction to amb   | _                     | 65                    | °C/W                  |      |

| TJ                | Junction temperature                  | _                     | 150                   |                       |      |

| Ts                | Storage temperature                   |                       | -55                   | 150                   | °C   |

| T∟                | Lead temperature (soldering, 10 se    | conds)                | _                     | 300                   |      |

## **Recommended Operating Conditions**

For proper operation the device should be used within the recommended conditions. All voltage parameters are absolute voltages referenced to  $V_{SS}$ . The  $V_{S}$  offset rating is tested with all supplies biased at a 15 V differential.

| Symbol           | De                                       | Min.                   | Max.                  | Units               |    |  |

|------------------|------------------------------------------|------------------------|-----------------------|---------------------|----|--|

| V <sub>B</sub>   | High side floating supply voltage (      | (Note 1)               | V <sub>S</sub> + 11.5 | V <sub>S</sub> + 20 |    |  |

| Vs               | High side floating supply offset voltage |                        |                       |                     |    |  |

| V <sub>HO</sub>  | High side output voltage (HOP, H         | Vs                     | V <sub>S</sub> + 20   |                     |    |  |

| $V_{LO}$         | Low side output voltage (LOP, LC         | V <sub>COM</sub>       | $V_{CC}$              |                     |    |  |

| V <sub>CC</sub>  | Low side and logic fixed supply vo       | 11.5                   | 20                    | V                   |    |  |

| COM              | Power ground                             | -5                     | 5                     |                     |    |  |

| V <sub>IN</sub>  | Logic input voltage (HIN, LIN and        | V <sub>SS</sub>        | V <sub>CC</sub>       |                     |    |  |

| V <sub>FLT</sub> | Fault input/output voltage (FAUL1        | V <sub>SS</sub>        | V <sub>CC</sub>       |                     |    |  |

| $V_{DSH}$        | High side DS pin input voltage           | V <sub>S</sub> - 2.0   | V <sub>B</sub>        |                     |    |  |

| V <sub>DSL</sub> | Low side DS pin input voltage            | V <sub>COM</sub> - 2.0 | V <sub>CC</sub>       |                     |    |  |

| T <sub>A</sub>   | Ambient temperature                      |                        | -40                   | 125                 | °C |  |

- Note 1: While internal circuitry is operational below the indicated supply voltages, the UV lockout disables the output drivers if the UV thresholds are not reached. A minimum supply voltage of 8V is recommended for the driver to operate safely under switching conditions at VS pin (refer to the "start-up sequence" in application section of this document)

- Note 2: Logic operational for V<sub>S</sub> from V<sub>SS</sub>-5 V to V<sub>SS</sub>+600 V or 1200 V. Logic state held for V<sub>S</sub> from V<sub>SS</sub>-5 V to V<sub>SS</sub>-V<sub>BS</sub>. For a negative spike on V<sub>B</sub> (referenced to V<sub>SS</sub>) of less than 200ns the IC will withstand a sustained peak of –40V under normal operation and an isolated event of up to -70V peak spike(Please refer to the Design Tip DT97-3 for more details).

## **Static Electrical Characteristics**

$V_{CC}$  = 15 V,  $V_{SS}$  = COM = 0 V,  $V_{S}$  = 600 V or 1200 V and  $T_{A}$  = 25 °C unless otherwise specified.

Pins: V<sub>CC</sub>, V<sub>SS</sub>, V<sub>B</sub>, V<sub>S</sub>

| Symbol              | Definition M                                                                   |     | Тур  | Max  | Units | Test Conditions                              |

|---------------------|--------------------------------------------------------------------------------|-----|------|------|-------|----------------------------------------------|

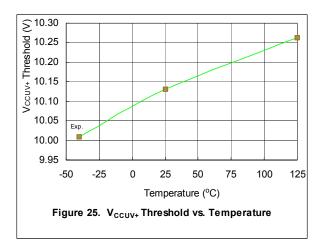

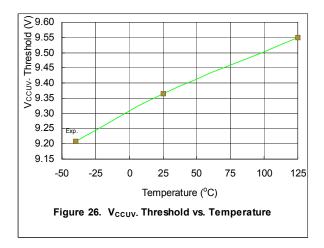

| V <sub>CCUV+</sub>  | V <sub>CC</sub> supply undervoltage positive going threshold                   | 9.3 | 10.2 | 11.4 |       |                                              |

| V <sub>CCUV</sub> - | V <sub>CC</sub> supply undervoltage negative going threshold                   | 8.7 | 9.3  | 10.3 |       |                                              |

| $V_{CCUVH}$         | V <sub>CC</sub> supply undervoltage lockout hysteresis                         | _   | 0.9  | _    | V     |                                              |

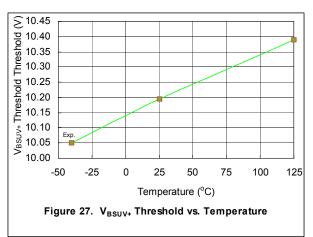

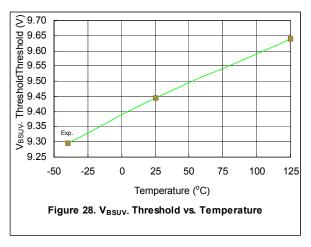

| $V_{BSUV}$ +        | (V <sub>B</sub> -V <sub>S</sub> ) supply undervoltage positive going threshold | 9.3 | 10.2 | 11.4 | ]     | V <sub>S</sub> = 0 V, V <sub>S</sub> = 600 V |

| $V_{BSUV}$          | (V <sub>B</sub> -V <sub>S</sub> ) supply undervoltage negative going threshold | 8.7 | 9.3  | 10.3 |       | or 1200 V                                    |

| $V_{BSUVH}$         | (V <sub>B</sub> -V <sub>S</sub> ) supply undervoltage lockout hysteresis       | _   | 0.9  | _    |       |                                              |

| I <sub>LK</sub>     | Offset supply leakage current                                                  |     | ı    | 50   | μA    | $V_B = V_S = 600 \text{ V or}$<br>1200 V     |

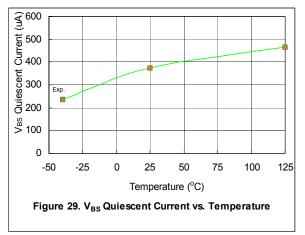

| $I_{QBS}$           | Quiescent V <sub>BS</sub> supply current                                       | _   | 400  | 800  |       | $V_{IN} = 0 \text{ V or } 3.3 \text{ V}$     |

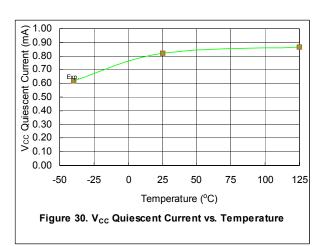

| I <sub>QCC</sub>    | Quiescent V <sub>CC</sub> supply current                                       |     | 0.7  | 2.5  | mA    | (No load)                                    |

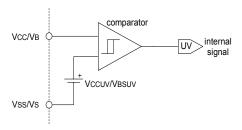

Note: Refer to Fig. 1

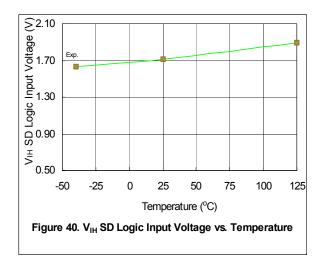

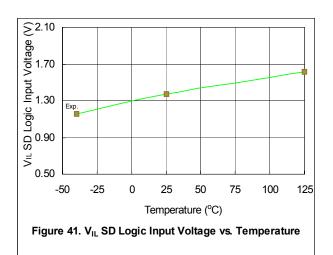

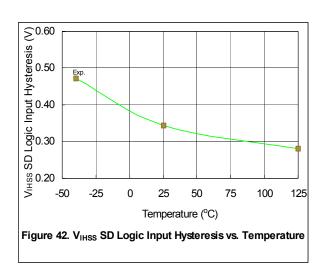

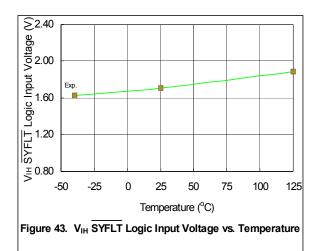

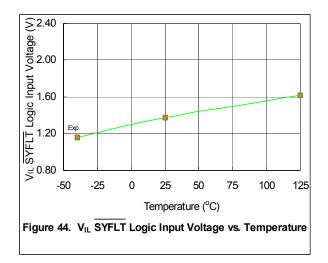

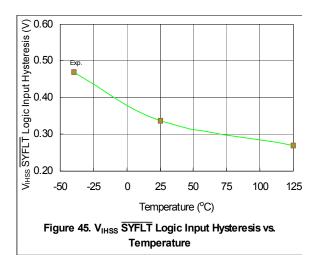

Pins: HIN, LIN, FLTCLR, FAULT/SD, SY FLT

| Symbol                                          | Definition                                      | Min | Тур | Max | Units | Test Conditions                |  |

|-------------------------------------------------|-------------------------------------------------|-----|-----|-----|-------|--------------------------------|--|

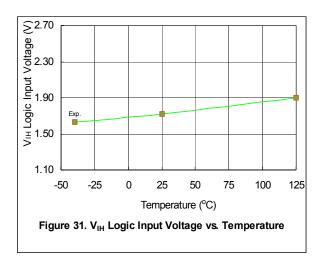

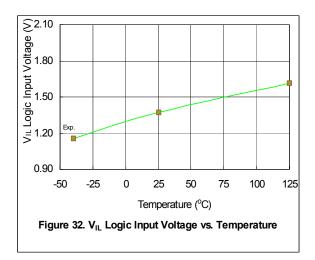

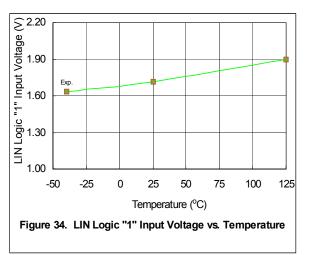

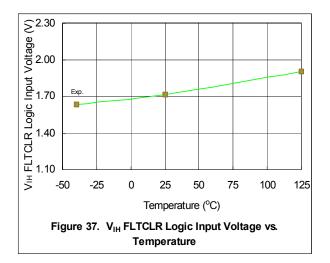

| $V_{IH}$                                        | Logic "1" input voltage                         | 2.0 | _   | _   |       |                                |  |

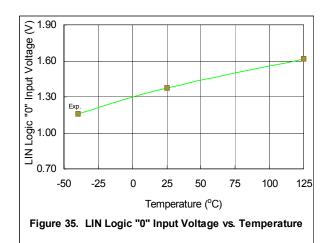

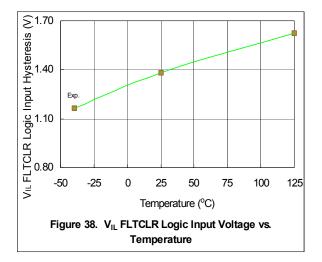

| V <sub>IL</sub>                                 | Logic "0" input voltage                         |     |     | 0.8 | V     | $V_{CC} = V_{CCUV}$<br>to 20 V |  |

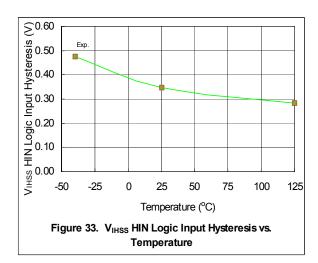

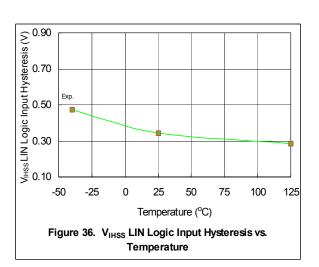

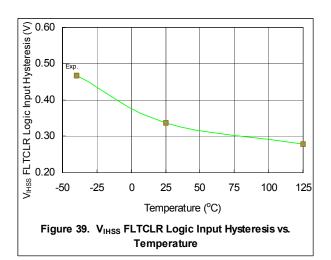

| $V_{IHSS}$                                      | Logic input hysteresis                          | 0.2 | 0.4 | _   |       | 10 20 V                        |  |

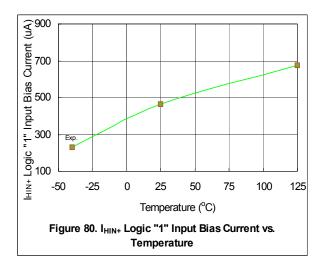

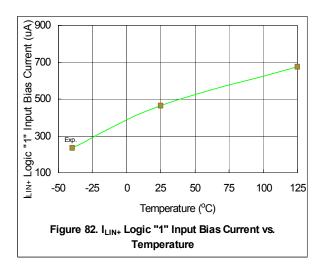

|                                                 | Logic "1" input bias current (HIN, LIN, FLTCLR) | _   | 330 | _   |       | V <sub>IN</sub> = 3.3 V        |  |

| I <sub>IN+</sub>                                | Logic "0" input bias current (FAULT/SD, SY_FLT) | 0   | _   | 1   |       | V <sub>IN</sub> – 3.3 V        |  |

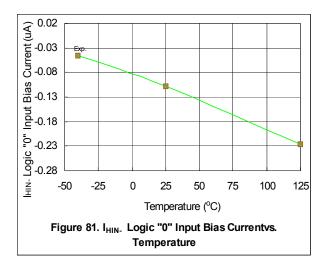

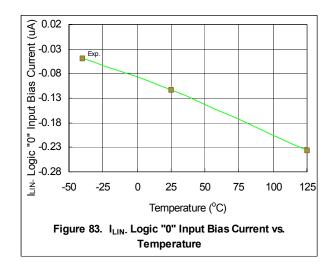

| 1                                               | Logic "0" input bias current                    | -1  | _   | 0   | μA    | V <sub>IN</sub> = 0 V          |  |

| I <sub>IN-</sub>                                | Logic "1" input bias current (FAULT/SD, SY_FLT) | -1  | _   | 0   |       |                                |  |

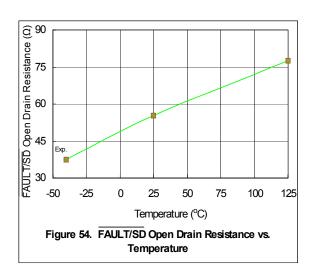

| $R_{ON,FLT}$                                    | FAULT/SD open drain resistance                  | _   | 60  | _   | 0     |                                |  |

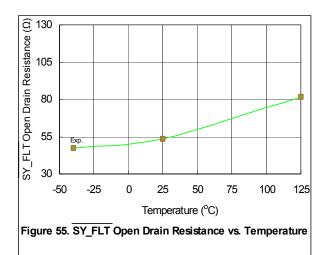

| R <sub>ON,SY</sub> SY_FLT open drain resistance |                                                 | _   | 60  | _   | Ω     | PW≤ 7 µs                       |  |

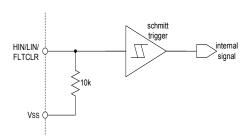

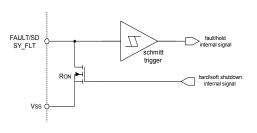

Note: Refer to Figs. 2 & 3

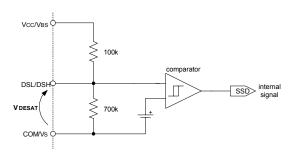

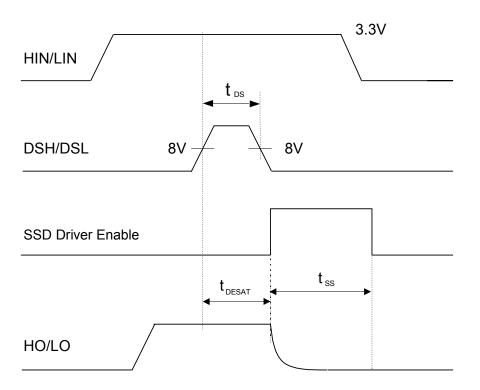

Pins: DSL, DSH

$V_{\text{DESAT}}$ ,  $I_{\text{DS}}$  and  $I_{\text{DSB}}$  parameters are referenced to COM and  $V_{\text{S}}$  respectively for DSL and DSH.

| Symbol            | Definition                                 | Min | Тур  | Max | Units | Test Conditions                  |

|-------------------|--------------------------------------------|-----|------|-----|-------|----------------------------------|

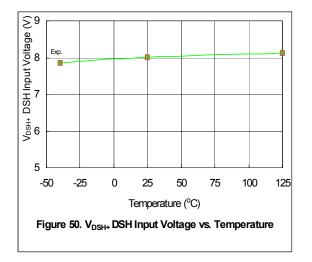

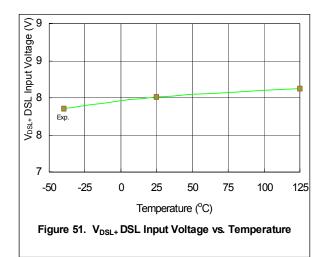

| $V_{DESAT+}$      | High desat input threshold voltage         | 7.2 | 8.0  | 8.8 |       |                                  |

| $V_{DESAT}$       | Low desat input threshold voltage          | 6.3 | 7.0  | 7.7 | V     | See Figs. 4,16                   |

| $V_{DSTH}$        | Desat input voltage hysteresis             |     | 1.0  | l   |       |                                  |

| I <sub>DS+</sub>  | High DSH or DSL input bias current (Note1) |     | 21   | ı   |       | $V_{DESAT} = V_{CC}$ or $V_{BS}$ |

| I <sub>DS</sub> - | Low DSH or DSL input bias current (Note1)  |     | -160 | _   | μA    | $V_{DESAT} = 0 V$                |

Note: Refer to Fig. 4

Note 1: An external decoupling 1KOhm resistor is required in order to limit current flowing in and out of DSH and DSL pin as result of switching noise coupled through the external de-saturation sensing diode

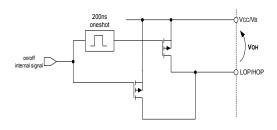

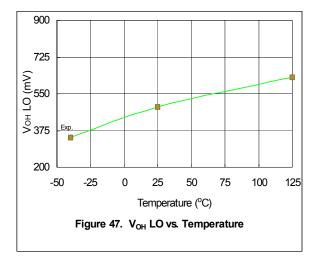

Pins: HOP, LOP

| Symbol           | Definition                                                                                        | Min | Тур | Max | Units | Test Conditions                                                                                                               |

|------------------|---------------------------------------------------------------------------------------------------|-----|-----|-----|-------|-------------------------------------------------------------------------------------------------------------------------------|

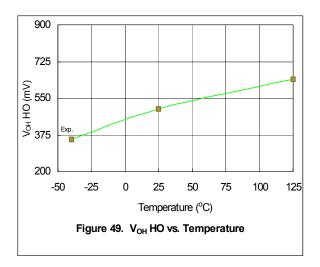

| V <sub>OH</sub>  | High level output voltage, V <sub>B</sub> – V <sub>HOP</sub> or V <sub>CC</sub> –V <sub>LOP</sub> | _   | 40  | 300 | mV    | I <sub>O</sub> = 20 mA                                                                                                        |

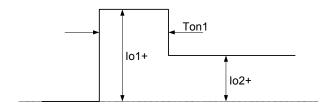

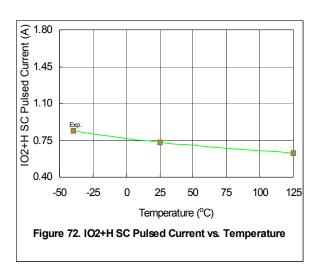

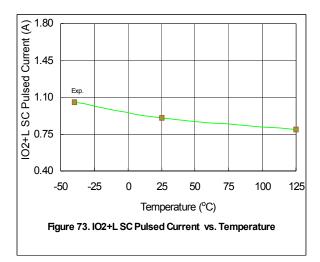

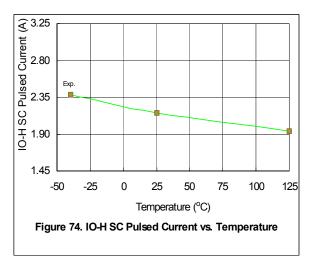

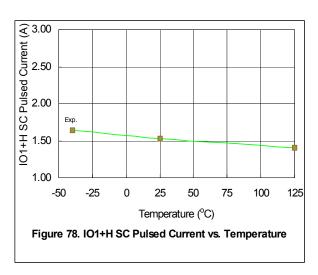

| I <sub>O1+</sub> | Output high first stage short circuit pulsed current                                              | 1   | 2   |     | A     | V <sub>HOP/LOP</sub> = 0 V, H <sub>IN</sub><br>or L <sub>IN</sub> = 1, PW≤<br>200 ns, resistive<br>load, see Fig. 8           |

| I <sub>O2+</sub> | Output high second stage short circuit pulsed current                                             | 0.5 | 1   | _   | A     | V <sub>HOP/LOP</sub> = 0 V, H <sub>IN</sub><br>or L <sub>IN</sub> = 1,<br>400 ns ≤PW≤ 10<br>µs, resistive load,<br>see Fig. 8 |

Note: Refer to Fig. 5

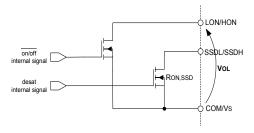

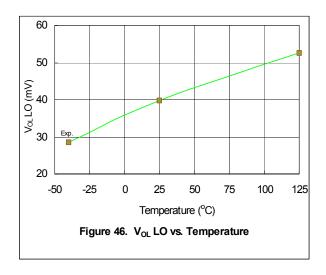

Pins: HON, LON, SSDH, SSDL

| Symbol              | Definition                                                     | Min | Тур | Max | Units | Test Conditions                                                               |

|---------------------|----------------------------------------------------------------|-----|-----|-----|-------|-------------------------------------------------------------------------------|

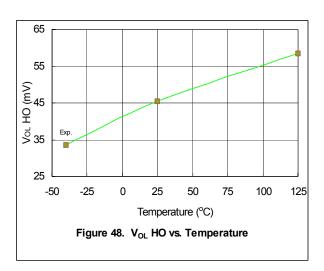

| V <sub>OL</sub>     | Low level output voltage, V <sub>HON</sub> or V <sub>LON</sub> | _   | 45  | 300 | mV    | I <sub>O</sub> = 20 mA                                                        |

| R <sub>ON,SSD</sub> | Soft Shutdown on resistance (Note 1)                           | _   | 90  | _   | Ω     | PW≤ 7 µs                                                                      |

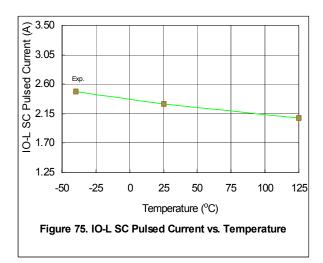

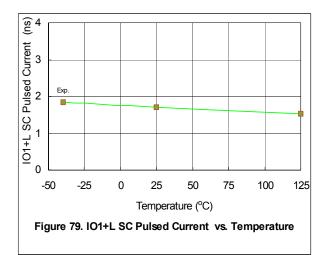

| I <sub>O-</sub>     | Output low short circuit pulsed current                        | 1.5 | 3   | _   | А     | $V_{HOP/LOP}$ = 15 V,<br>H <sub>IN</sub> or L <sub>IN</sub> = 0, PW≤<br>10 µs |

Note: Refer to Fig. 6

Note 1: SSD operation only

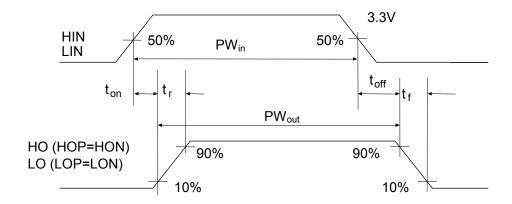

## **AC Electrical Characteristics**

$V_{\text{CC}}$  =  $V_{\text{BS}}$  = 15 V,  $V_{\text{S}}$  =  $V_{\text{SS}}$  and  $T_{\text{A}}$  = 25 °C unless otherwise specified.

| Symbol                          | Definition                                                       | Min. | Тур. | Max.  | Units | Test Conditions                                                                 |

|---------------------------------|------------------------------------------------------------------|------|------|-------|-------|---------------------------------------------------------------------------------|

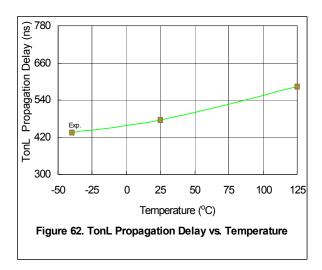

| t <sub>on</sub>                 | Turn on propagation delay                                        | 220  | 440  | 660   |       | V <sub>IN</sub> = 0 & 1, V <sub>S</sub> = 0 V to 600 V or                       |

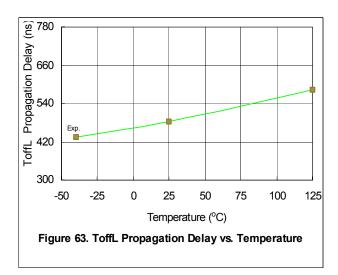

| t <sub>off</sub>                | Turn off propagation delay                                       | 220  | 440  | 660   |       | 1200 V,                                                                         |

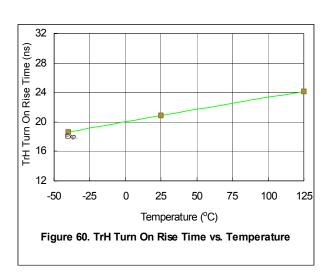

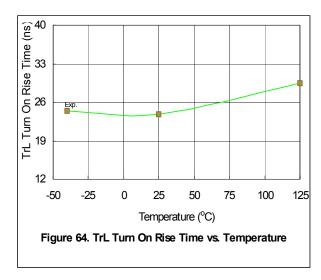

| t <sub>r</sub>                  | Turn on rise time (C <sub>LOAD</sub> =1 nF)                      |      | 24   | _     |       | HOP shorted to HON, LOP                                                         |

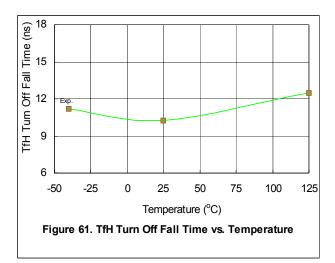

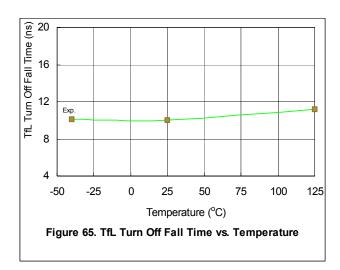

| t <sub>f</sub>                  | Turn off fall time (C <sub>LOAD</sub> =1 nF)                     | _    | 7    | _     |       | shorted to LON, Fig. 7                                                          |

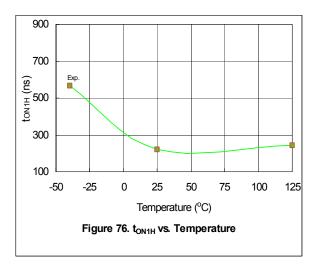

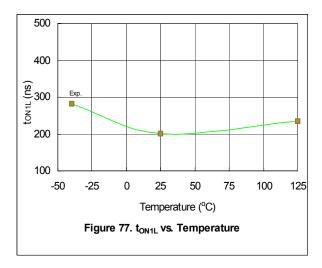

| t <sub>on1</sub>                | Turn on first stage duration time                                | 120  | 200  | 280   |       | Fig. 8                                                                          |

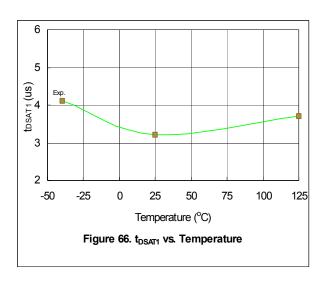

| t <sub>DESAT1</sub>             | DSH to HO soft shutdown propagation delay at HO turn on          | 2000 | 3300 | 4600  |       | V <sub>HIN</sub> = 1 V                                                          |

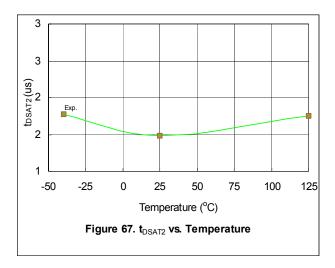

| t <sub>DESAT2</sub>             | DSH to HO soft shutdown propagation delay after blanking         | 1050 | _    | _     |       | V <sub>DESAT</sub> = 15 V, Fig. 10                                              |

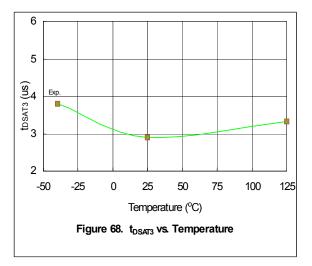

| t <sub>DESAT3</sub>             | DSL to LO soft shutdown propagation delay at LO turn on          | 2000 | 3300 | 4600  |       | V <sub>LIN</sub> = 1 V                                                          |

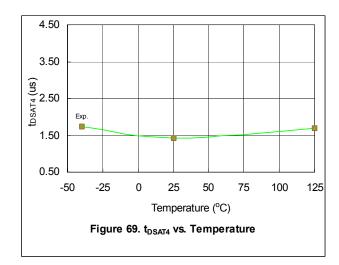

| t <sub>DESAT4</sub>             | DSL to LO soft shutdown propagation delay after blanking         | 1050 | _    | _     |       | V <sub>DESAT</sub> = 15 V, Fig. 10                                              |

| t <sub>DS</sub>                 | Soft shutdown minimum pulse width of desat                       | 1000 | _    | _     |       | Fig. 9                                                                          |

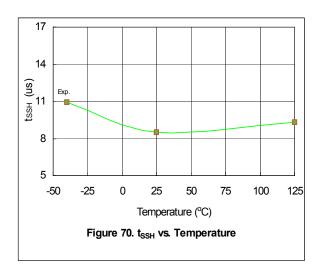

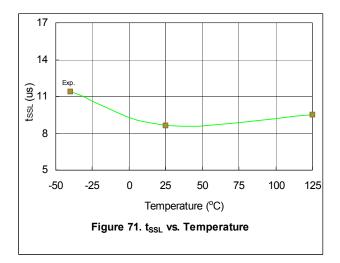

| t <sub>SS</sub>                 | Soft shutdown duration period                                    | 5700 | 9250 | 13500 |       | V <sub>DS</sub> =15 V, Fig. 9                                                   |

| t <sub>SY_FLT</sub> , DESAT1    | DSH to SY_FLT propagation delay at HO turn on                    |      | 3600 | _     | ns    | V <sub>HIN</sub> = 1 V                                                          |

| t <sub>SY_FLT</sub> ,<br>DESAT2 | DSH to SY_FLT propagation delay after blanking                   | 1300 | _    | _     |       | V <sub>DS</sub> = 15 V, Fig. 10                                                 |

| t <sub>SY_FLT</sub> , DESAT3    | DSL to SY_FLT propagation delay at LO turn on                    |      | 3050 | _     |       | V <sub>LIN</sub> = 1 V                                                          |

| t <sub>SY_FLT</sub> , DESAT4    | DSL to SY_FLT propagation delay after blanking                   | 1050 | _    | _     |       | V <sub>DESAT</sub> =15 V, Fig. 10                                               |

| t <sub>BL</sub>                 | DS blanking time at turn on                                      | _    | 3000 | _     |       | V <sub>HIN</sub> = V <sub>LIN</sub> = 1 V, V <sub>DESAT</sub> =15 V,<br>Fig. 10 |

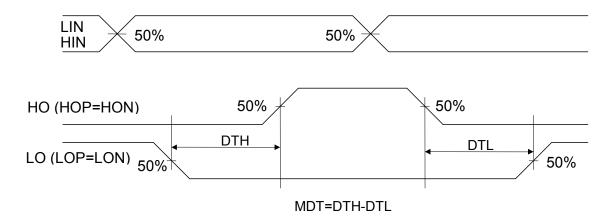

| Dea                             | dtime/Delay Matching Characteristics                             |      |      | _     |       |                                                                                 |

| DT                              | Deadtime                                                         |      | 330  | _     | ]     | Fig. 11                                                                         |

| MDT                             | Deadtime matching, MDT=DTH-DTL                                   | _    | _    | 75    |       | External DT = 0 s, Fig. 11                                                      |

| PDM                             | Propagation delay matching,<br>Max (ton, toff) – Min (ton, toff) | _    | _    | 75    |       | External DT > 500 ns, Fig. 7                                                    |

Note: For high side PWM, HIN pulse must be ≥1µs

Figure 1: Undervoltage Diagram

Figure 2: HIN, LIN and FLTCLR Diagram

Figure 3: FAULT/SD and SY\_FLT Diagram

Figure 4: DSH and DSL Diagram

Figure 5: HOP and LOP Diagram

Figure 6: HON, LON, SSDH and SSDL Diagram

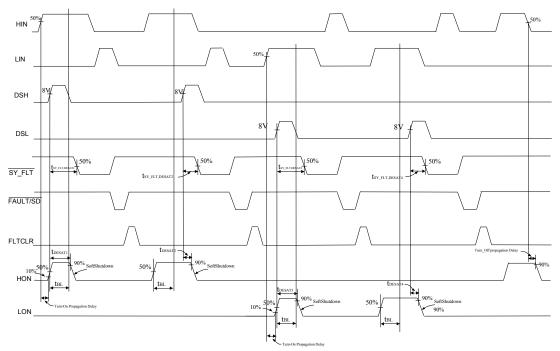

Figure 7: Switching Time Waveforms

Figure 8: Output Source Current

Figure 9: Soft Shutdown Timing Waveform

Figure 10: Desat Timing

Figure 11: Internal Deadtime Timing

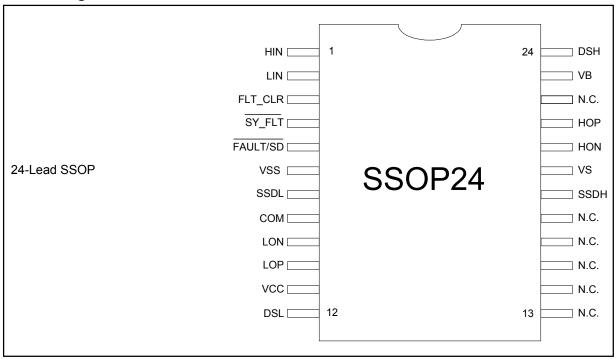

## **Lead Assignments**

## **Lead Definitions**

| Symbol          | Description                                                                                                                                                                                                               |  |  |  |  |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| V <sub>CC</sub> | Low side gate driver supply                                                                                                                                                                                               |  |  |  |  |  |

| V <sub>SS</sub> | Logic ground                                                                                                                                                                                                              |  |  |  |  |  |

| HIN             | Logic input for high side gate driver outputs (HOP/HON)                                                                                                                                                                   |  |  |  |  |  |

| LIN             | Logic input for low side gate driver outputs (LOP/LON)                                                                                                                                                                    |  |  |  |  |  |

| FAULT/SD        | Dual function (in/out) active low pin. Refer to Figs. 15, 17, and 18. As an output, indicates fault condition. As an input, shuts down the outputs of the gate driver regardless H <sub>IN</sub> /L <sub>IN</sub> status. |  |  |  |  |  |

| SY_FLT          | Dual function (in/out) active low pin. Refer to Figs. 15, 17, and 18. As an output, indicates SSD sequence is occurring. As an input, an active low signal freezes both output status.                                    |  |  |  |  |  |

| FLT_CLR         | Fault clear active high input. Clears latched fault condition (see Fig. 17)                                                                                                                                               |  |  |  |  |  |

| LOP             | Low side driver sourcing output                                                                                                                                                                                           |  |  |  |  |  |

| LON             | Low side driver sinking output                                                                                                                                                                                            |  |  |  |  |  |

| DSL             | Low side IGBT desaturation protection input                                                                                                                                                                               |  |  |  |  |  |

| SSDL            | Low side soft shutdown                                                                                                                                                                                                    |  |  |  |  |  |

| COM             | Low side driver return                                                                                                                                                                                                    |  |  |  |  |  |

| $V_B$           | High side gate driver floating supply                                                                                                                                                                                     |  |  |  |  |  |

| HOP             | High side driver sourcing output                                                                                                                                                                                          |  |  |  |  |  |

| HON             | High side driver sinking output                                                                                                                                                                                           |  |  |  |  |  |

| DSH             | High side IGBT desaturation protection input                                                                                                                                                                              |  |  |  |  |  |

| SSDH            | High side soft shutdown                                                                                                                                                                                                   |  |  |  |  |  |

| Vs              | High side floating supply return                                                                                                                                                                                          |  |  |  |  |  |

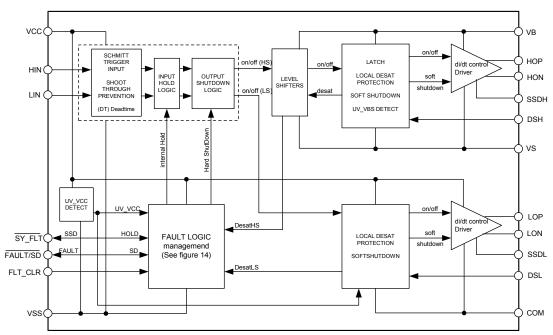

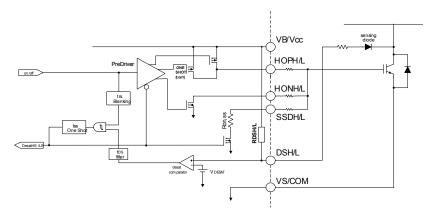

## **FUNCTIONAL BLOCK DIAGRAM**

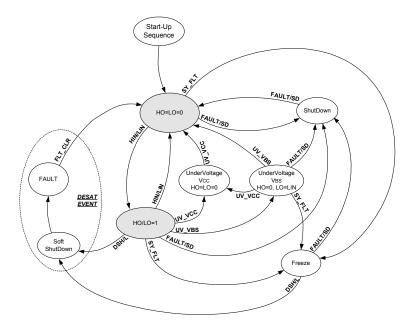

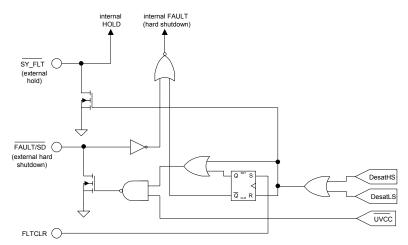

## **STATE DIAGRAM**

| Sta | ble State                    | Tei | mporary State     | Sy | stem Variable |

|-----|------------------------------|-----|-------------------|----|---------------|

| _   | FAULT                        | _   | SOFT SHUTDOWN     | _  | FLT_CLR       |

| _   | HO=LO=0 (Normal operation)   | -   | START UP SEQUENCE | _  | HIN/LIN       |

| _   | HO/LO=1 (Normal operation)   |     |                   | _  | UV_VCC        |

| _   | UNDERVOLTAGE V <sub>CC</sub> |     |                   | _  | UV_VBS        |

| _   | SHUTDOWN (SD)                |     |                   | _  | DSH/L         |

| _   | UNDERVOLTAGE V <sub>BS</sub> |     |                   | _  | SY_FLT        |

| _   | FREEZE                       |     |                   | _  | FAULT/SD      |

|     |                              |     |                   |    |               |

|     |                              |     |                   |    |               |

NOTE 1: A change of logic value of the signal labeled on lines (system variable) generates a state transition.

NOTE 2: Exiting from UNDERVOLTAGE V<sub>BS</sub> state, the HO goes high only if a rising edge event happens in H<sub>IN</sub>.

| HO/LO Status                         | HOP/LOP                      | HON/LON                                          | SSDH/SSDL |  |  |  |  |  |

|--------------------------------------|------------------------------|--------------------------------------------------|-----------|--|--|--|--|--|

| 0                                    | HiZ                          | 0                                                | HiZ       |  |  |  |  |  |

| 1                                    | 1                            | HiZ                                              |           |  |  |  |  |  |

| SSD                                  | HiZ                          | HiZ HiZ                                          |           |  |  |  |  |  |

| LO/HO                                | Output follow                | Output follows inputs (in=1->out=1, in=0->out=0) |           |  |  |  |  |  |

| LO <sub>n-1</sub> /HO <sub>n-1</sub> | Output keeps previous status |                                                  |           |  |  |  |  |  |

IR2214 Logic Table: Output Drivers Status Description

|                       | INPUTS          |                 | UTS      | INPUT/                                               | Undervoltage Yes: V< UV threshold No: V> UV threshold X: don't care |     | OUTPUTS         |                   |                   |

|-----------------------|-----------------|-----------------|----------|------------------------------------------------------|---------------------------------------------------------------------|-----|-----------------|-------------------|-------------------|

| Operation             | Hin             | Lin             | FLT_CLR  | SY_FLT<br>SSD: desat (out)<br>HOLD: freezing<br>(in) | FAULT/SD SD: shutdown (in) FAULT: diagnostic (out)                  | Vcc | V <sub>BS</sub> | НО                | LO                |

| Shutdown              | Х               | Х               | X        | X                                                    | 0 (SD)                                                              | Х   | Х               | 0                 | 0                 |

| Fault Clear           | H <sub>IN</sub> | L <sub>IN</sub> | <u>_</u> | Note 1                                               | _ (FAULT)                                                           | No  | No              | НО                | LO                |

| Fault Cleared         | H <sub>IN</sub> | L <sub>IN</sub> | 1        | Х                                                    | 1 (Note 2)                                                          | No  | No              | НО                | LO                |

|                       | 1               | 0               | 0        | 1                                                    | 1                                                                   | No  | No              | 1                 | 0                 |

| Normal<br>Operation   | 0               | 1               | 0        | 1                                                    | 1                                                                   | No  | No              | 0                 | 1                 |

|                       | 0               | 0               | 0        | 1                                                    | 1                                                                   | No  | No              | 0                 | 0                 |

| Anti Shoot<br>Through | 1               | 1               | 0        | 1                                                    | 1                                                                   | No  | No              | 0                 | 0                 |

| Soft<br>Shutdown      | 1               | 0               | 0        | ₹ (SSD)                                              | 1                                                                   | No  | No              | SSD               | 0                 |

| (entering)            | 0               | 1               | 0        | (SSD)                                                | 1                                                                   | No  | No              | 0                 | SSD               |

| Soft<br>Shutdown      | Х               | Х               | 0        | √ (SSD)                                              | → (FAULT)                                                           | No  | No              | 0                 | 0                 |

| (finishing)           | Х               | Х               | 0        | _ (SSD)                                              | ₹ (FAULT)                                                           | No  | No              | 0                 | 0                 |

| Freeze                | Х               | Х               | Х        | 0 (HOLD)                                             | 1                                                                   | No  | No              | HO <sub>n-1</sub> | LO <sub>n-1</sub> |

| Undervoltage          | Х               | L <sub>IN</sub> | Х        | 1                                                    | 1                                                                   | No  | Yes             | 0                 | LO                |

|                       | Х               | Х               | Х        | 1                                                    | 0 (FAULT)                                                           | Yes | Х               | 0                 | 0                 |

Note 1: SY\_FLT automatically resets after the SSD event is over and FLT\_CLR is not required. In order to avoid the FLT\_CLR conflicting with the SSD procedure, FLT\_CLR should not be operated while SY\_FLT is active.

Note 2: Holding FLT\_CLR high all time will not allow the gate driver to latch the FAULT status and migth compromise power system protection.

## **1 Features Description**

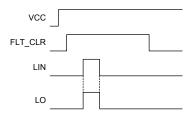

#### 1.1 Start-Up Sequence

At power supply start-up, it is recommended to keep the FLT\_CLR pin active until the supply voltages are properly established. This prevents spurious diagnostic signals being generated.

When the bootstrap supply topology is used for supplying the floating high side stage, the following start-up sequence is recommended (see also Fig. 12):

- 1. Set V<sub>CC</sub>

- 2. Set FLT\_CLR pin to HIGH level,

- Set LIN pin to HIGH level and charge the bootstrap capacitor,

- 4. Release LIN pin to LOW level,

- 5. Release FLT\_CLR pin to LOW level.

Figure 12 Start-Up Sequence

A minimum 15 µs LIN and FLT-CLR pulse is required. A minimum supply voltage of 8V is recommended for the driver to operate safely under switching conditions at VS pin. At lower supply the gate driving capability decreases and might become not sufficient to counteract switching charge injected to the outputs.

#### 1.2 Normal Operation Mode

After the start-up sequence has completed, the device becomes fully operative (see grey blocks in the State Diagram).

HIN and LIN produce driver outputs to switch accordingly, while the input logic monitors the input signals and deadtime (DT) prevent shoot-through events from occurring.

#### 1.3 Shutdown

The system controller can asynchronously command the Hard Shutdown (HSD) through the 3.3 V compatible CMOS I/O FAULT/SD pin. This event is not latched.

In a multi-phase system, FAULT/SD signals are or-ed so the controller or one of the gate drivers can force the simultaneous shutdown of the other gate drivers through the same pin.

#### 1.4 Fault Management

The IR2114/ IR2214 is able to manage supply failure (undervoltage lockout) and transistor desaturation (on both the low and high side switches).

#### 1.4.1 Undervoltage (UV)

The undervoltage protection function disables the driver's output stage which prevents the power device from being driven when the input voltage is less than the undervoltage threshold. Both the low side ( $V_{\rm CC}$  supplied) and the floating side ( $V_{\rm BS}$  supplied) are controlled by a dedicate undervoltage function.

An undervoltage event on the  $V_{\rm CC}$  pin (when  $V_{\rm CC} < UV_{\rm VCC}$ .) generates a diagnostic signal by forcing the FAULT/SD pin low (see FAULT/SD section and Fig. 14). This event disables both the low side and floating drivers and the diagnostic signal holds until the undervoltage condition is over. The fault condition is not latched and the FAULT/SD pin is released once  $V_{\rm CC}$  becomes higher than  $UV_{\rm VCC+}$ .

The  $V_{BS}$  undervoltage protection works by disabling only the floating driver. Undervoltage on  $V_{BS}$  does not prevent the low side driver from activating its output nor does it generate diagnostic signals. The  $V_{BS}$  undervoltage condition ( $V_{BS} < UV_{VBS-}$ ) latches the high side output stage in the low state.  $V_{BS}$  must exceed the  $UV_{VBS+}$  threshold to return the device to its normal operating mode. To turn on the floating driver,  $H_{IN}$  must be reasserted high (rising edge event on  $H_{IN}$  is required).

#### 1.4.2 Power Devices Desaturation

Different causes can generate a power inverter failure (phase and/or rail supply short-circuit, overload conditions induced by the load, etc.). In all of these fault conditions, a large increase in current results in the IGBT.

The IR2114/ IR2214 fault detection circuit monitors the IGBT emitter to collector voltage ( $V_{\text{CE}}$ ) (an external high voltage diode is connected between the IGBT's collector and the ICs DSH or DSL pins). A high current in the IGBT may cause the transistor to desaturate; this condition results in an increase of  $V_{\text{CE}}$ .

Once in desaturation, the current in the power transistor can be as high as 10 times the nominal current. Whenever the transistor is switched off, this high current generates relevant voltage transients in the power stage that need to be smoothed out in order to avoid destruction (by over-voltage). The gate driver is able to control the transient condition by smoothly turning off the desaturated transistor with its integrated soft shutdown (SSD) protection.

## 1.4.3 Desaturation Detection: DSH/L Function

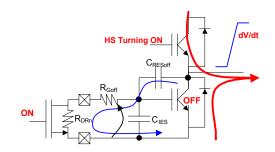

Figure 13 shows the structure of the desaturation sensing and soft shutdown block. This configuration is the same for both the high and low side output stages.

Figure 13: High and Low Side Output Stage

Figure 14: Fault Management Diagram

The external sensing diode should have BV > 600 V (IR2114) or > 1200 V (IR2214), low stray capacitance and low recovery current (in order to minimize noise coupling and switching delays). The diode is biased by an internal pull-up resistor  $R_{DSH/L}$  (equal to  $V_{CC}/I_{DS-}$  or  $V_{BS}/I_{DS-}$  for IR2114 or IR2214). When  $V_{CE}$  increases, the voltage at the DSH or DSL pin increases too. Being internally biased to the local supply, the DSH/DSL voltage is automatically clamped. When DSH/DSL exceeds the  $V_{\text{DESAT+}}$  threshold, the comparator triggers (see Fig. 13). The comparator's output is filtered in order to avoid false desaturation detection by externally induced noise; pulses shorter than t<sub>DS</sub> are filtered out. To avoid detecting a false desaturation event during IGBT turn on, the desaturation circuit is disabled by a blanking signal (T<sub>BL</sub>, see blanking block in Fig. 13). This time is the estimated maximum IGBT turn on time and must be not exceeded by proper gate resistance sizing. When the IGBT is not completely saturated after T<sub>BL</sub>, desaturation is detected and the driver will turn off.

Eligible desaturation signals initiate the SSD sequence. While in SSD, the driver's output goes to a high impedance state and the SSD pull-down is activated to turn off the IGBT through the SSDH/SSDL pin. The SY\_FLT output pin (active low, see Fig. 14) reports the gate driver status during the SSD sequence ( $t_{\rm SS}$ ). Once

the SSD has finished, SY\_FLT releases, and the gate <u>driver generates</u> a FAULT signal (see the FAULT/SD section) by activating the FAULT/SD pin. This generates a hard shutdown for both the high and low output stages (HO=LO=low). Each driver is latched low until the fault is cleared (see FLT\_CLR).

Figure 14 shows the fault management circuit. In this diagram DesatHS and DesatLS are two internal signals that come from the output stages (see Fig. 13).

It must be noted that while in SSD, both the undervoltage fault and external SD are masked until the end of SSD. Desaturation protection is working independently by the other control pin and it is disabled only when the output status is off.

For the purpose of sensing the power transistor desaturation, the collector voltage is monitored (an external high voltage diode is connected between the IGBT's collector and the IC's DSH or DSL pin). The diode is normally biased by an internal pull up resistor connected to the local supply line (VB or VCC). When the transistor is "on" the diode is conducting and the amount of current flowing in the circuit is determined by the internal pull up resistor value.

In the high side circuit, the desaturation biasing current may become relevant for dimensioning the bootstrap capacitor (see Fig. 19). In fact, a pull up resistor with a low resistance may result in a high current the significantly discharges the bootstrap capacitor. For that reason, the typical pull up resistor value is on the order of  $100~\mathrm{k}\Omega$ . This is the value of the internal pull up.

While the impedance of the DSH/DSL pins is very low when the transistor is on (low impedance path through the external diode down to the power transistor), the impedance is only controlled by the pull up resistor when the transistor is off. In that case, relevant dV/dt generated at VS node might push the DSH/DSL pins outside the recommended operating conditions. A resistor of minimum 1000 Ohm is required in series to the desat diode to limit the amount of current injected or sourced at DSH/DSL pin.

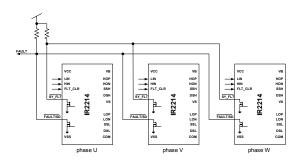

# **1.4.4 Fault Management in Multi-Phase Systems** In a system with two or more gate drivers the IR2x14 devices must be connected as shown in Fig. 15.

Figure 15: IR2214 Used in a 3 Phase Application

$\overline{SY\_FLT}$ : The bi-directional  $\overline{SY\_FLT}$  pins communicate each other through a local network. The logic signal is active low. The device that detects the IGBT desaturation activates the  $\overline{SY\_FLT}$ , which is then read by the other gate drivers. When  $\overline{SY\_FLT}$  is active all the drivers hold their output state regardless of the input signals  $(H_{IN}, L_{IN})$  they receive from the controller (freeze state). This feature is particularly important in phase-to-phase short circuit where two IGBTs are involved; in

fact, while one is softly shutting-down, the other must be prevented from hard shutdown to avoid exiting SSD. In the freeze state, the frozen drivers are not completely inactive because desaturation detection still takes the highest priority. SY\_FLT communication has been designed for creating a local network between the drivers. There is no need to wire SY\_FLT to the controller.

FAULT/SD: The bi-directional FAULT/SD pins communicate with each other and with the system controller. The logic signal is active low. When low, the FAULT/SD signal commands the outputs to go off by hard shutdown. There are three events that can force FAULT/SD low:

- Desaturation detection event: the FAULT/SD pin is latched low when SSD is over, and only a FLT\_CLR signal can reset it,

- Undervoltage on V<sub>CC</sub>: the FAULT/SD pin is forced low and held until the undervoltage is active (not latched).

- 3. FAULT/SD is externally driven low either from the controller or from another IR2x14 device. This event is *not latched*; therefore the FLT\_CLR cannot disable it. Only when FAULT/SD becomes high the device returns to its normal operating mode.

#### 1.5 Output Stage

The structure is shown in Fig. 13 and consists of two turn on stages and one turn off stage. When the driver turns on the IGBT (see Fig. 8), a first stage is activated while an additional stage is maintained in the active state for a limited time (ton1). This feature boosts the total driving capability in order to accommodate both a fast gate charge to the plateau voltage and dV/dt control in switching.

At turn off, a single n-channel sinks up to 3 A ( $I_{O-}$ ) and offers a low impedance path to prevent the self-turn on due to the parasitic Miller capacitance in the power switch.

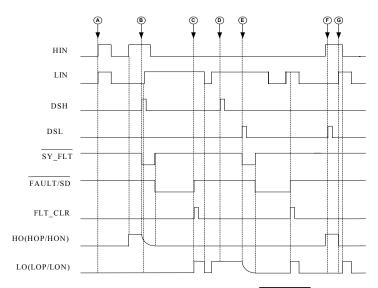

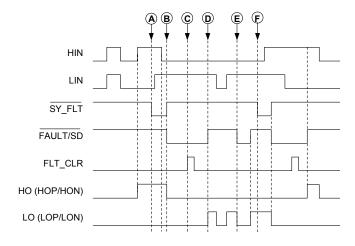

## 1.6 Timing and Logic State Diagrams Description

The following figures show the input/output logic diagram. Figure 16 shows the  $\overline{SY\_FLT}$  and  $\overline{FAULT/SD}$  signals as outputs, whereas Fig. 17 shows them as inputs.

Figure 16: I/O Timing Diagram with SY\_FLT and FAULT/SD as Output

Figure 17: I/O Logic Diagram with SY\_FLT and FAULT/SD as Input

Referred to the timing diagram of Fig. 16:

- When the input signals are on together the outputs go off (anti-shoot through),

- B. The HO signal is on and the high side IGBT desaturates, the HO turn off softly while the SY\_FLT stays low. When SY\_FLT goes high the FAULT/SD goes low. While in SSD, if LIN goes up, LO does not change (freeze),

- C. When FAULT/SD is latched low (see FAULT/SD section) FLT\_CLR can disable it and the outputs go back to follow the inputs,

- D. The DSH goes high but this is not read because HO is off,

- E. The LO signal is on and the low side IGBT desaturates, the low side behaviour is the same as described in point B,

- F. The DSL goes high but this is not read as LO is off.

- G. As point A (anti-shoot through).

Referred to the timing diagram Fig. 17:

- A. The device is in the hold state, regardless of input variations. The hold state results as SY FLT is forced low externally.

- B. The device outputs go off by hard shutdown, externally commanded. A through B is the same sequence adopted by another IR2x14x device in SSD procedure.

- Externally driven low FAULT/SD (shutdown state) cannot be disabled by forcing FLT\_CLR (see FAULT/SD section),

- The FAULT/SD is released and the outputs go back to follow the inputs.

- E. Externally driven low FAULT/SD: outputs go off by hard shutdown (like point B),

15

F. As point A and B but for the low side output.

## 2 Sizing Tips

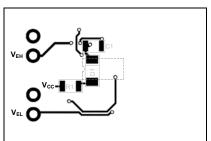

#### 2.1 Bootstrap Supply

The  $V_{BS}$  voltage provides the supply to the high side driver circuitry of the gate driver. This supply sits on top of the  $V_{S}$  voltage and so it must be floating. The bootstrap method is used to generate the  $V_{BS}$  supply and can be used with IR2114)/ IR2214 drivers. The bootstrap supply is formed by a diode and a capacitor as connected in Fig. 18.

Figure 18: Bootstrap Supply Schematic

This method has the advantage of being simple and low cost but may force some limitations on duty-cycle and on-time since they are limited by the requirement to refresh the charge in the bootstrap capacitor. Proper capacitor choice can reduce drastically these limitations.

#### 2.2 Bootstrap Capacitor Sizing

To size the bootstrap capacitor, the first step is to establish the minimum voltage drop  $(\Delta V_{BS})$  that we have to guarantee when the high side IGBT is on.

If  $V_{GEmin}$  is the minimum gate emitter voltage we want to maintain, the voltage drop must be:

$$\Delta V_{BS} \leq V_{CC} - V_F - V_{GE\, \mathrm{min}} - V_{CEon}$$

under the condition,

$$V_{GF \min} > V_{RSUV-}$$

where  $V_{CC}$  is the IC voltage supply,  $V_F$  is bootstrap diode forward voltage,  $V_{CEon}$  is emitter-collector voltage of low side IGBT, and  $V_{BSUV}$  is the high-side supply undervoltage negative going threshold.

Now we must consider the influencing factors contributing  $V_{\text{BS}}$  to decrease:

- IGBT turn on required gate charge (Q<sub>G</sub>),

- IGBT gate-source leakage current (I<sub>LK\_GE</sub>),

- Floating section quiescent current (IQBS),

- Floating section leakage current (ILK),

- Bootstrap diode leakage current (ILK\_DIODE),

- Desat diode bias when on (IDS-),

- Charge required by the internal level shifters (Q<sub>LS</sub>); typical 20 nC,

## IR2114SSPBF/IR2214SSPbF

- Bootstrap capacitor leakage current (I<sub>LK CAP</sub>),

- High side on time (THON).

$I_{LK\_CAP}$  is only relevant when using an electrolytic capacitor and can be ignored if other types of capacitors are used. It is strongly recommend using at least one low ESR ceramic capacitor (paralleling electrolytic and low ESR ceramic may result in an efficient solution).

Then we have:

$$\begin{split} Q_{TOT} &= Q_G + Q_{LS} + (I_{LK\_GE} + I_{QBS} + \\ &+ I_{LK} + I_{LK\_DIODE} + I_{LK\_CAP} + I_{DS-}) \cdot T_{HON} \end{split}$$

The minimum size of bootstrap capacitor is:

$$C_{BOOT\,\text{min}} = \frac{Q_{TOT}}{\Delta V_{BS}}$$

An example follows using IR2214SS:

a) using a 25 A @ 125 °C 1200 V IGBT (IRGP30B120KD):

- $I_{QBS}$  = 800  $\mu$ A (datasheet IR2214);

- $I_{LK}$  = 50  $\mu$ A (see Static Electrical Characteristics);

- Q<sub>LS</sub> = 20 nC

- Q<sub>G</sub> = 160 nC (datasheet IRGP30B120KD);

- $I_{LK\_GE}$  = 100 nA (datasheet IRGP30B120KD);

- $I_{LK\_DIODE}$  = 100  $\mu$ A (reverse recovery <100 ns);

- I<sub>LK\_CAP</sub> = 0 (neglected for ceramic capacitor);

I<sub>DS</sub> = 150 µA (see Static Electrical Characteristics);

- $T_{HON} = 100 \ \mu s$ .

And:

- V<sub>CC</sub> = 15 V

- $V_F = 1 \text{ V}$

- $V_{CEonmax} = 3.1 \text{ V}$

- $V_{GEmin} = 10.5 \text{ V}$

the maximum voltage drop  $\Delta V_{BS}$  becomes

$$\Delta V_{BS} \le V_{CC} - V_F - V_{GEmin} - V_{CEon} =$$

= 15 V-1 V-10.5 V-3.1 V= 0.4 V

And the bootstrap capacitor is:

$$C_{BOOT} \ge \frac{290 \ nC}{0.4 \ V} = 725 \ nF$$

**NOTICE:**  $V_{CC}$  has been chosen to be 15 V. Some IGBTs may require a higher supply to work correctly with the bootstrap technique. Also  $V_{CC}$  variations must be accounted in the above formulas.

16

# International TOR Rectifier

#### 2.3 Some Important Considerations

Voltage Ripple: There are three different cases to consider (refer to Fig. 18).

•  $I_{LOAD}$  < 0 A; the load current flows in the low side IGBT (resulting in  $V_{CEon}$ ).

$$V_{RS} = V_{CC} - V_F - V_{CEon}$$

In this case we have the lowest value for  $V_{\text{BS}}$ . This represents the worst case for the bootstrap capacitor sizing. When the IGBT is turned off, the  $V_{\text{S}}$  node is pushed up by the load current until the high side freewheeling diode is forwarded biased.

• I  $_{\text{LOAD}}$  = 0 A; the IGBT is not loaded while being on and  $V_{\text{CE}}$  can be neglected

$$V_{RS} = V_{CC} - V_F$$

$\cdot$  I<sub>LOAD</sub> > 0 A; the load current flows through the freewheeling diode

$$V_{RS} = V_{CC} - V_F + V_{FP}$$

In this case we have the highest value for  $V_{\text{BS}}.$  Turning on the high side IGBT,  $I_{\text{LOAD}}$  flows into it and  $V_{\text{S}}$  is pulled up. To minimize the risk of undervoltage, the bootstrap capacitor should be sized according to the  $I_{\text{LOAD}} < 0$  A case.

Bootstrap Resistor: A resistor ( $R_{boot}$ ) is placed in series with the bootstrap diode (see Fig. 18) in order to limit the current when the bootstrap capacitor is initially charged. We suggest not exceeding 10  $\Omega$  to avoid increasing the  $V_{BS}$  time-constant. The minimum on time for charging the bootstrap capacitor or for refreshing its charge must be verified against this time-constant.

Bootstrap Capacitor: For high  $T_{HON}$  designs where an electrolytic capacitor is used, its ESR must be considered. This parasitic resistance forms a voltage divider with R<sub>boot</sub>, which generats a voltage step on V<sub>BS</sub> at the first charge of bootstrap capacitor. The voltage step and the related speed (dV<sub>BS</sub>/dt) should be limited. As a general rule, ESR should meet the following constraint.

$$\frac{ESR}{ESR + R_{ROOT}} \cdot V_{CC} \le 3V$$

A parallel combination of a small ceramic capacitor and a large electrolytic capacitor is normally the best compromise, the first capacitor posses a fast time constant and limits the  $dV_{BS}/dt$  by reducing the equivalent resistance. The second capacitor provides a large capacitance to maintain the  $V_{BS}$  voltage drop within the desired  $\Delta V_{BS}.$

## IR2114SSPBF/IR2214SSPbF

Bootstrap Diode: The diode must have a BV > 600 V or 1200 V and a fast recovery time (trr < 100 ns) to

minimize the amount of charge fed back from the bootstrap capacitor to V<sub>CC</sub> supply.

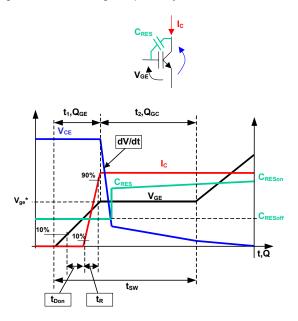

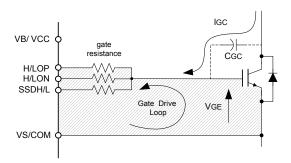

#### 2.4 Gate Resistances

The switching speed of the output transistor can be controlled by properly sizing the resistors controlling the turn-on and turn-off gate currents. The following section provides some basic rules for sizing the resistors to obtain the desired switching time and speed by introducing the equivalent output resistance of the gate driver ( $R_{DRp}$  and  $R_{DRn}$ ).

The example shown uses IGBT power transistors and Figure 19 shows the nomenclature used in the following paragraphs. In addition,  $V_{ge}$  indicates the plateau voltage,  $Q_{gc}$  and  $Q_{ge}$  indicate the gate to collector and gate to emitter charge respectively.

Figure 19: Nomenclature

#### 2.5 Sizing The Turn-On Gate Resistor

Switching-Time: For the matters of the calculation included hereafter, the switching time  $t_{\rm sw}$  is defined as the time spent to reach the end of the plateau voltage (a total  $Q_{\rm gc}+Q_{\rm ge}$  has been provided to the IGBT gate). To obtain the desired switching time the gate resistance can be sized starting from  $Q_{\rm ge}$  and  $Q_{\rm gc}$ , Vcc,  $V_{\rm ge}$  (see Fig. 20):

$$I_{avg} = \frac{Q_{gc} + Q_{ge}}{t_{sw}}$$

and

$$R_{TOT} = \frac{Vcc - V_{ge}^*}{I_{av\sigma}}$$

Figure 20: R<sub>Gon</sub> Sizing

where

$$R_{TOT} = R_{DRp} + R_{Gon}$$

$R_{Gon}$  = gate on-resistor

$R_{DRp}$  = driver equivalent on-resistance

When  $R_{Gon} > 7 \Omega$ ,  $R_{DRp}$  is defined by

$$R_{DRp} = \begin{cases} \frac{Vcc}{I_{o1+}} + \frac{Vcc}{I_{o2+}} \left(\frac{t_{SW}}{t_{on1}} - 1\right) & when \quad t_{SW} > t_{on1} \\ \frac{Vcc}{I_{o1+}} & when \quad t_{SW} \leq t_{on1} \end{cases}$$

(I<sub>O1+</sub>,I<sub>O2+</sub> and t<sub>on1</sub> from "Static Electrical Characteristics").

Table 1 reports the gate resistance size for two commonly used IGBTs (calculation made using typical datasheet values and assuming  $V_{\text{CC}}$ = 15 V).

Output Voltage Slope: The turn-on gate resistor  $R_{\text{Gon}}$  can be sized to control the output slope  $(dV_{\text{OUT}}/dt)$ . While the output voltage has a nonlinear behaviour, the maximum output slope can be approximated by:

$$\frac{dV_{out}}{dt} = \frac{I_{avg}}{C_{RESoff}}$$

inserting the expression yielding lavg and rearranging:

$$R_{TOT} = \frac{Vcc - V_{ge}^{*}}{C_{RESoff} \cdot \frac{dV_{out}}{dt}}$$

As an example, table 2 shows the sizing of gate resistance to get  $dV_{out}/dt=5$  V/ns when using two popular IGBTs (typical datasheet values are used and  $V_{CC}=15$  V is assumed).

**NOTICE**: Turn on time must be lower than  $T_{BL}$  to avoid improper desaturation detection and SSD triggering.

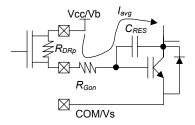

## 2.6 Sizing the Turn-Off Gate Resistor

The worst case in sizing the turn-off resistor  $R_{\text{Goff}}$  is when the collector of the IGBT in the off state is forced to commutate by an external event (e.g., the turn-on of the companion IGBT). In this case the dV/dt of the output node induces a parasitic current through  $C_{\text{RESoff}}$  flowing in  $R_{\text{Goff}}$  and  $R_{\text{DRn}}$  (see Fig. 21). If the voltage

drop at the gate exceeds the threshold voltage of the

IGBT, the device may self turn on, causing large oscillation and relevant cross conduction.

Figure 21: R<sub>Goff</sub> Sizing: Current Path When Low Side is Off and High Side Turns On

The transfer function between the IGBT collector and the IGBT gate then becomes:

$$\frac{V_{ge}}{V_{de}} = \frac{s \cdot (R_{Goff} + R_{DRn}) \cdot C_{RESoff}}{1 + s \cdot (R_{Goff} + R_{DRn}) \cdot (C_{RESoff} + C_{IES})}$$

Which yields to a high pass filter with a pole at:

$$1/\tau = \frac{1}{(R_{Goff} + R_{DRn}) \cdot (C_{RESoff} + C_{IES})}$$

As a result, when  $\tau$  is faster than the collector rise time (to be verified after calculation) the transfer function can be approximated by:

$$\frac{V_{ge}}{V_{de}} = s \cdot (R_{Goff} + R_{DRn}) \cdot C_{RESoff}$$

So that

$$V_{ge} = (R_{Goff} + R_{DRn}) \cdot C_{RESoff} \cdot \frac{dV_{de}}{dt}$$

in the time domain.

Then the condition:

$$V_{th} > V_{ge} = (R_{Goff} + R_{DRn}) \cdot C_{RESoff} \frac{dV_{out}}{dt}$$

must be verified to avoid spurious turn on.

Rearranging the equation yields:

$$R_{Goff} < \frac{V_{th}}{C_{RESoff} \cdot \frac{dV}{dt}} - R_{DRn}$$

In any case, the worst condition for unwanted turn on is with very fast steps on the IGBT collector.

In that case, the collector to gate transfer function can be approximated with the capacitor divider:

$$V_{ge} = V_{de} \cdot \frac{C_{\textit{RESoff}}}{(C_{\textit{RESoff}} + C_{\textit{IES}})}$$

which is driven only by IGBT characteristics.

As an example, table 3 reports  $R_{Goff}$  (calculated with the above mentioned disequation) for two popular IGBTs to withstand  $dV_{out}/dt = 5 \ V/ns$ .

**NOTICE:** The above-described equations are intended to approximate a way to size the gate resistance. A more accurate sizing may provide more precise device and PCB (parasitic) modelling.

| IGBT           | Qge   | Qgc   | Vge* | tsw    | lavg   | Rtot | RGon → std commercial value                         | Tsw     |

|----------------|-------|-------|------|--------|--------|------|-----------------------------------------------------|---------|

| IRGP30B120K(D) | 19 nC | 82 nC | 9 V  | 400 ns | 0.25 A | 24 Ω | RTOT - RDRp = 12.7 $\Omega \rightarrow$ 10 $\Omega$ | →420 ns |

| IRG4PH30K(D)   | 10 nC | 20 nC | 9 V  | 200 ns | 0.15 A | 40 Ω | RTOT - RDRp = $32.5 \Omega \rightarrow 33 \Omega$   | →202 ns |

Table 1: t<sub>sw</sub> Driven R<sub>Gon</sub> Sizing

| IGBT           | Qge   | Qgc   | Vge* | CRESoff | Rtot | RGon → std commercial value                       | dVout/dt  |

|----------------|-------|-------|------|---------|------|---------------------------------------------------|-----------|

| IRGP30B120K(D) | 19 nC | 82 nC | 9 V  | 85 pF   | 14 Ω | RTOT - RDRp = $6.5 \Omega \rightarrow 8.2 \Omega$ | →4.5 V/ns |

| IRG4PH30K(D)   | 10 nc | 20 nC | 9 V  | 14 pF   | 85 Ω | RTOT - RDRp = 78 $\Omega \rightarrow$ 82 $\Omega$ | →5 V/ns   |

Table 2: dV<sub>OUT</sub>/dt Driven R<sub>Gon</sub> Sizing

| IGBT           | Vth(min) | CRESoff | RGoff        |

|----------------|----------|---------|--------------|

| IRGP30B120K(D) | 4        | 85 pF   | RGoff ≤ 4 Ω  |

| IRG4PH30K(D)   | 3        | 14 pF   | RGoff ≤ 35 Ω |

Table 3: R<sub>Goff</sub> Sizing

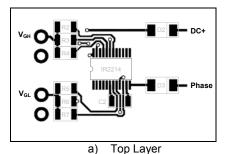

## **3 PCB Layout Tips**

#### 3.1 Distance from High to Low Voltage

The IR2x14/1 pin out maximizes the distance between floating (from DC- to DC+) and low voltage pins. It's strongly recommended to place components tied to floating voltage on the high voltage side of device ( $V_B$ ,  $V_S$  side) while the other components are placed on the opposite side.

#### 3.2 Ground Plane

To minimize noise coupling, the ground plane must not be placed under or near the high voltage floating side.

#### 3.3 Gate Drive Loops

Current loops behave like antennas and are able to receive and transmit EM noise. In order to reduce the EM coupling and improve the power switch turn on/off performances, gate drive loops must be reduced as much as possible. Figure 22 shows the high and low side gate loops.

Moreover, current can be injected inside the gate drive loop via the IGBT collector-to-gate parasitic capacitance. The parasitic auto-inductance of the gate loop contributes to developing a voltage across the gate-emitter, increasing the possibility of self turn-on. For this reason, it is strongly recommended to place the three gate resistances close together and to minimize the loop area (see Fig. 22).

Figure 22: gate drive loop

#### 3.4 Supply Capacitors

The IR2x14x output stages are able to quickly turn on an IGBT, with up to 2 A of output current. The supply capacitors must be placed as close as possible to the device pins (V $_{\rm CC}$  and V $_{\rm SS}$  for the ground tied supply, V $_{\rm B}$  and V $_{\rm S}$  for the floating supply) in order to minimize parasitic inductance/resistance.

## 3.5 Routing and Placement Example

Figure 23 shows one of the possible layout solutions using a 3 layer PCB. This example takes into account all the previous considerations. Placement and routing for supply capacitors and gate resistances in the high and low voltage side minimize the supply path loop and the gate drive loop. The bootstrap diode is placed under the device to have the cathode as close as possible to the bootstrap capacitor and the anode far from high voltage and close to  $V_{\rm CC}$ .

b) Bottom Layer

Figure 23: layout example

Information below refers to Fig. 23: Bootstrap section: R1, C1, D1 High side gate: R2, R3, R4 High side Desat: D2 Low side supply: C2

Low side gate: R5, R6, R7 Low side Desat: D3

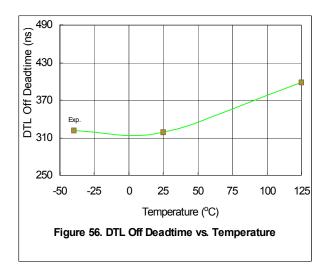

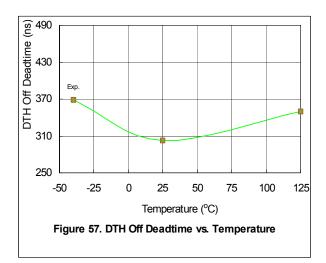

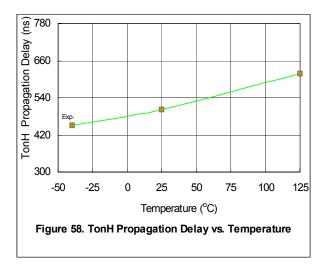

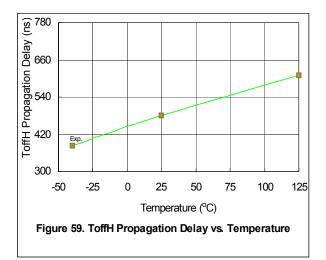

Figures 25-83 provide information on the experimental performance of the IR2114/ IR2214 HVIC. The line plotted in each figure is generated from actual lab data. A large number of individual samples from multiple wafer lots were tested at three temperatures (-40 °C, 25 °C, and 125 °C) in order to generate the experimental (Exp.) curve. The line labeled Exp. consist of three data points (one data point at each of the tested temperatures) that have been connected together to illustrate the understood trend. The individual data points on the curve were determined by calculating the averaged experimental value of the parameter (for a given temperature).

<u>www.irf.com</u> 21

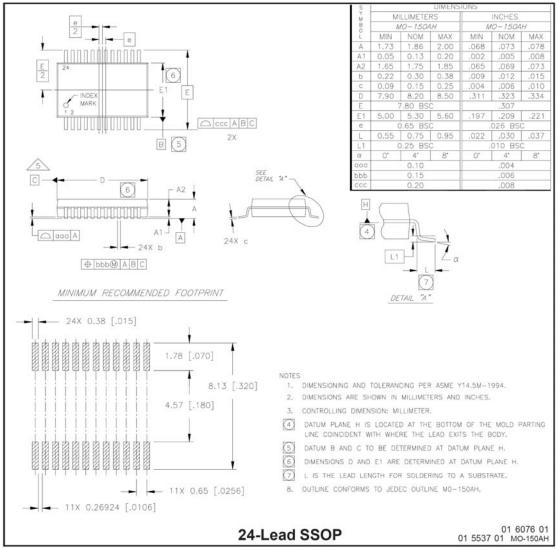

## **Case Outline**

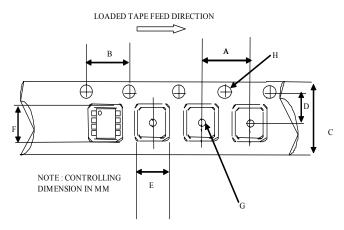

CARRIER TAPE DIMENSION FOR 24SSOP:2000 units per reel

| OFFICE PROPERTY OF STREET |       |       |          |       |  |  |  |

|---------------------------|-------|-------|----------|-------|--|--|--|

|                           | Me    | etric | Imperial |       |  |  |  |

| Code                      | Min   | Max   | Min      | Max   |  |  |  |

| Α                         | 11.90 | 12.10 | 0.468    | 0.476 |  |  |  |

| В                         | 3.90  | 4.10  | 0.153    | 0.161 |  |  |  |

| С                         | 15.70 | 16.30 | 0.618    | 0.641 |  |  |  |

| D                         | 7.40  | 7.60  | 0.291    | 0.299 |  |  |  |

| E                         | 8.30  | 8.50  | 0.326    | 0.334 |  |  |  |

| F                         | 8.50  | 8.70  | 0.334    | 0.342 |  |  |  |

| G                         | 1.50  | n/a   | 0.059    | n/a   |  |  |  |

| Н                         | 1.50  | 1.60  | 0.059    | 0.062 |  |  |  |

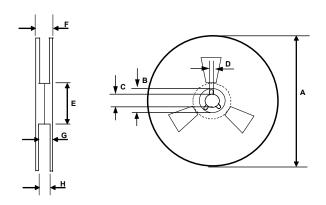

REEL DIMENSIONS FOR 24SSOP

| TELE DIMENSIONS I ON 240001 |        |        |          |        |  |  |  |

|-----------------------------|--------|--------|----------|--------|--|--|--|

|                             | Me     | etric  | Imperial |        |  |  |  |

| Code                        | Min    | Max    | Min      | Max    |  |  |  |

| Α                           | 329.60 | 330.25 | 12.976   | 13.001 |  |  |  |

| В                           | 20.95  | 21.45  | 0.824    | 0.844  |  |  |  |

| С                           | 12.80  | 13.20  | 0.503    | 0.519  |  |  |  |

| D                           | 1.95   | 2.45   | 0.767    | 0.096  |  |  |  |

| E                           | 98.00  | 102.00 | 3.858    | 4.015  |  |  |  |

| F                           | n/a    | 22.40  | n/a      | 0.881  |  |  |  |

| G                           | 18.50  | 21.10  | 0.728    | 0.830  |  |  |  |

| Н                           | 16.40  | 18.40  | 0.645    | 0.724  |  |  |  |

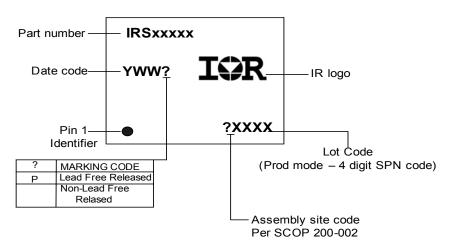

#### LEAD-FREE PART MARKING INFORMATION

#### ORDER INFORMATION

24-Lead SSOP IR2114SSPbF 24-Lead SSOP IR2214SSPbF

24-Lead SSOP Tape & Reel IR2114SSPbF 24-Lead SSOP Tape & Reel IR2214SSPbF

WORLDWIDE HEADQUARTERS: 233 Kansas Street, El Segundo, CA 90245 Tel: (310) 252-7105

This part has been qualified per industrial level

<a href="http://www.irf.com">http://www.irf.com</a> Data and specifications subject to change without notice. 4/2008